Me, Myself and I

Ich und mein Ego - heh lässt sich nicht wirklich gut aus dem Englischen übersetzen...

C/C#/C++

Programming

Programmieren

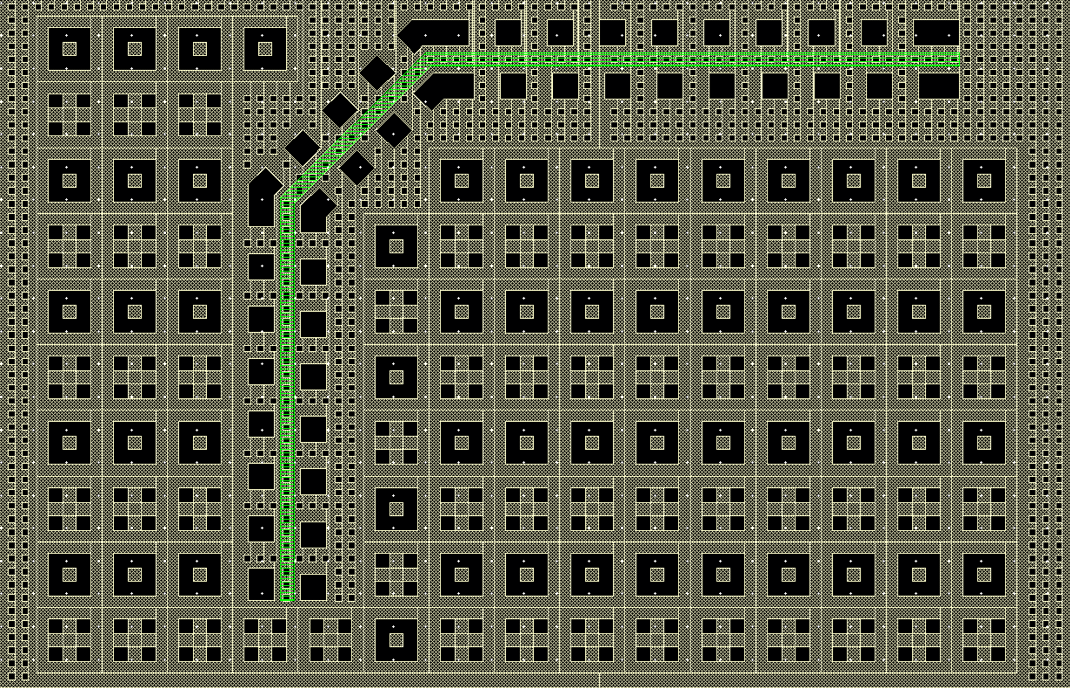

KiCad

Student Education

Studenten Ausbildung

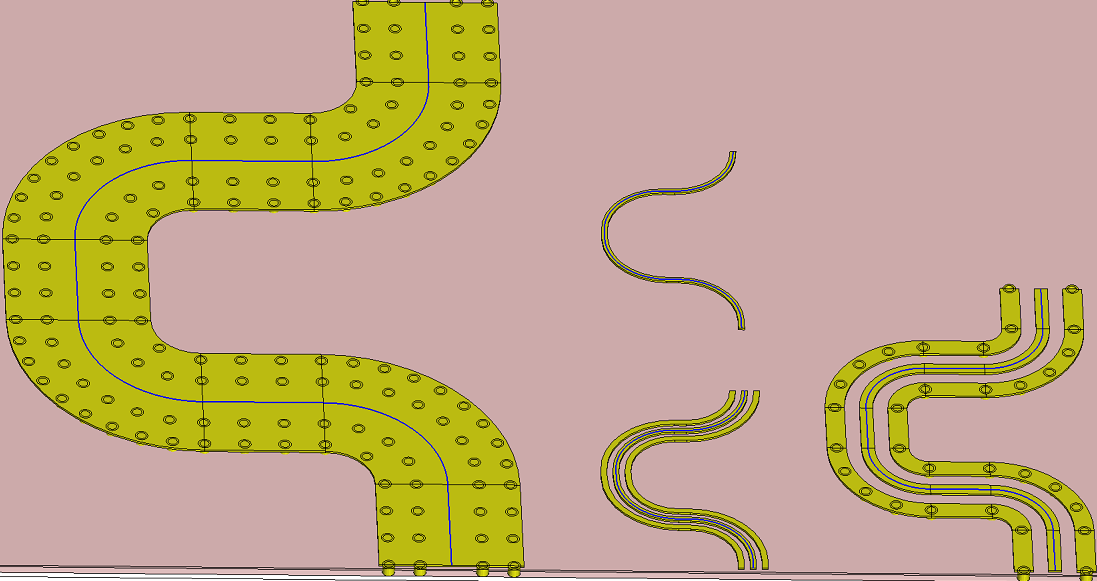

FreeCAD

Altium

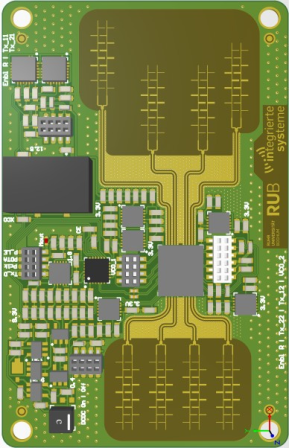

COM-RADAR

3D Printing

3D Druck

Valestra

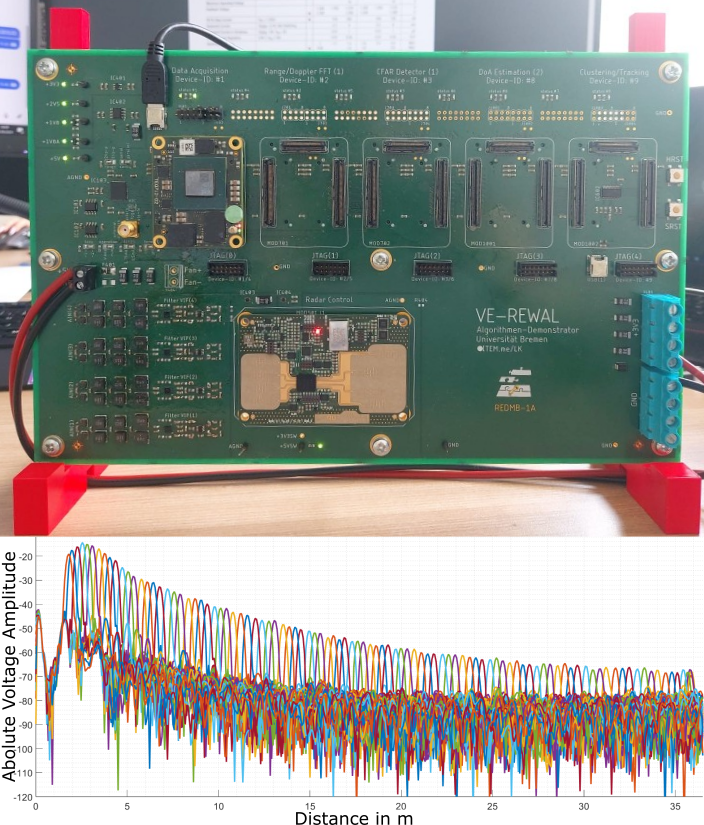

VE-REWAL

Student Education

Studenten-ausbildung

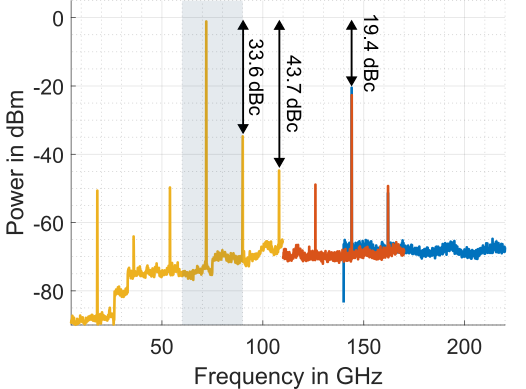

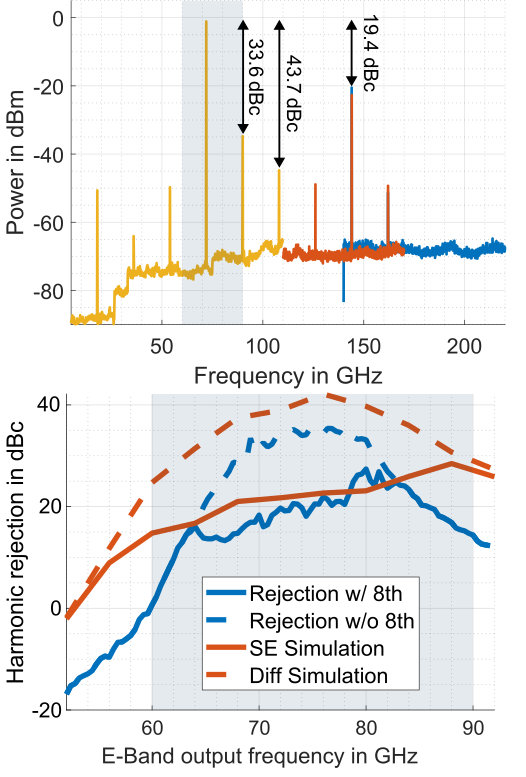

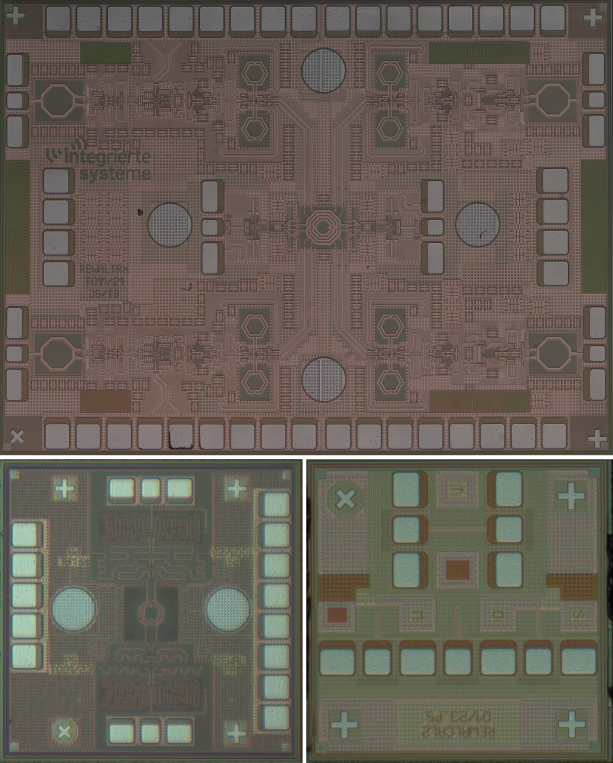

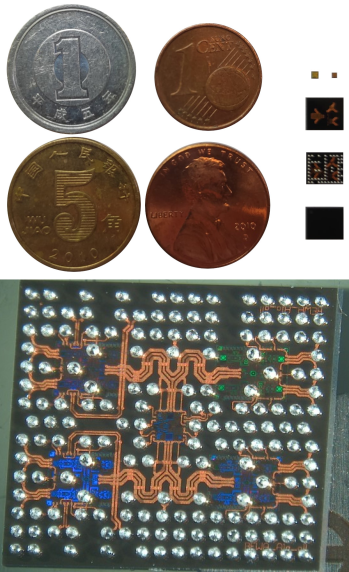

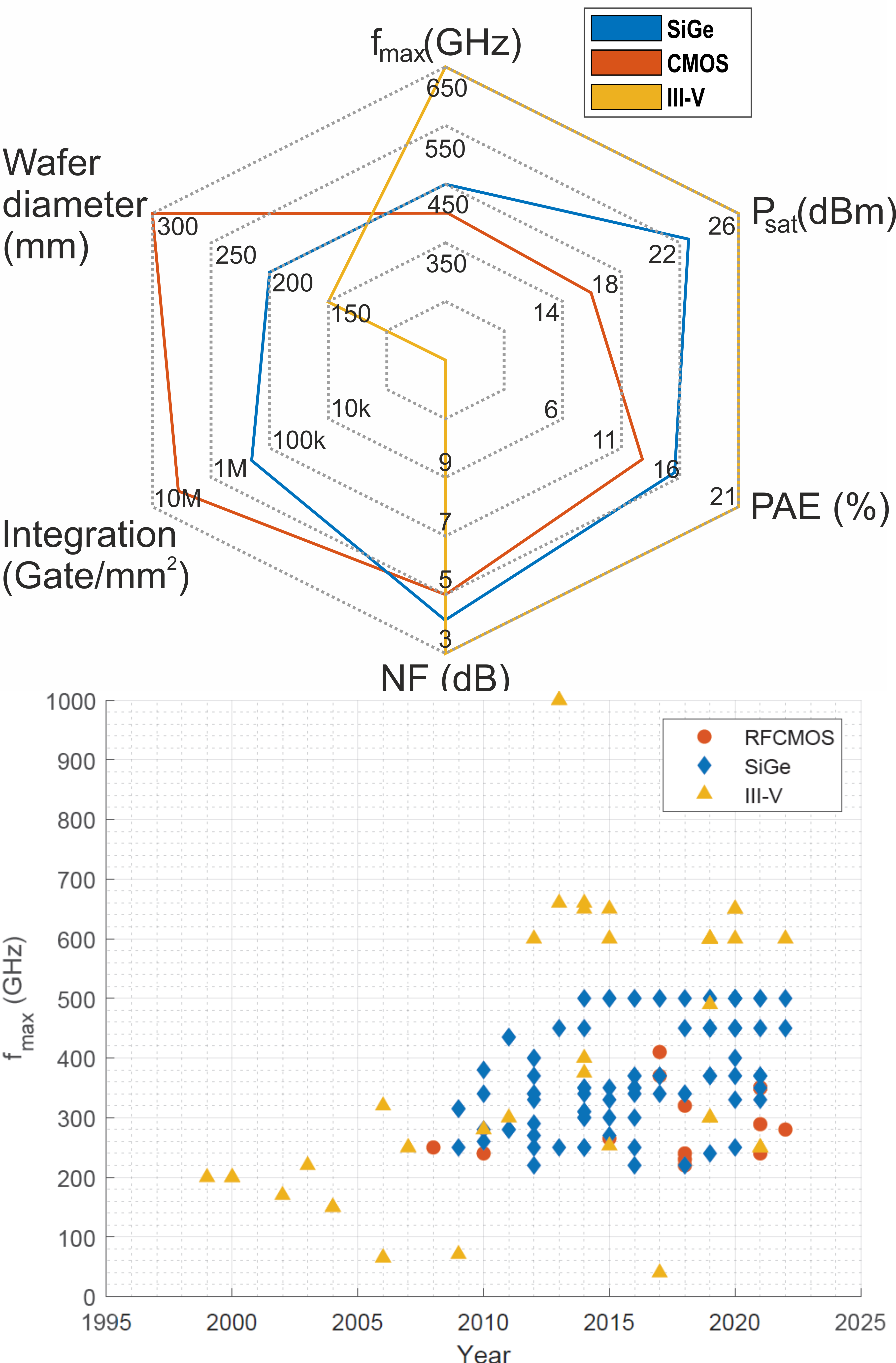

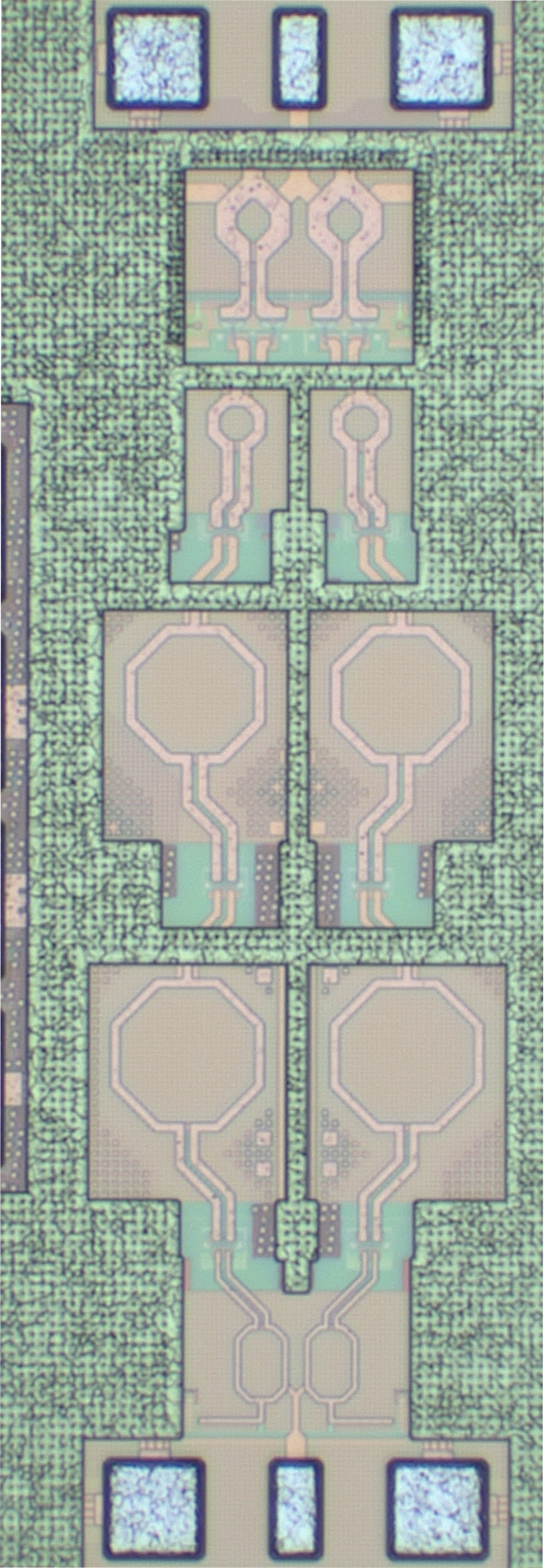

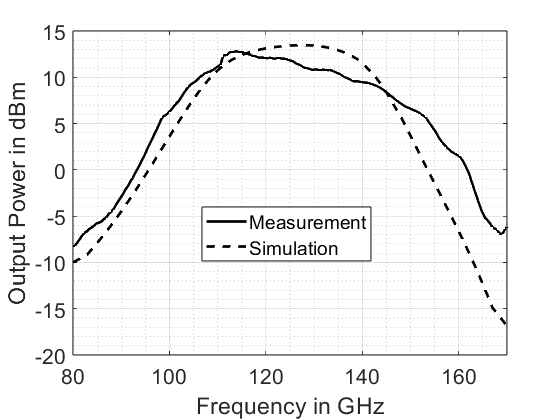

140 GHz CMOS

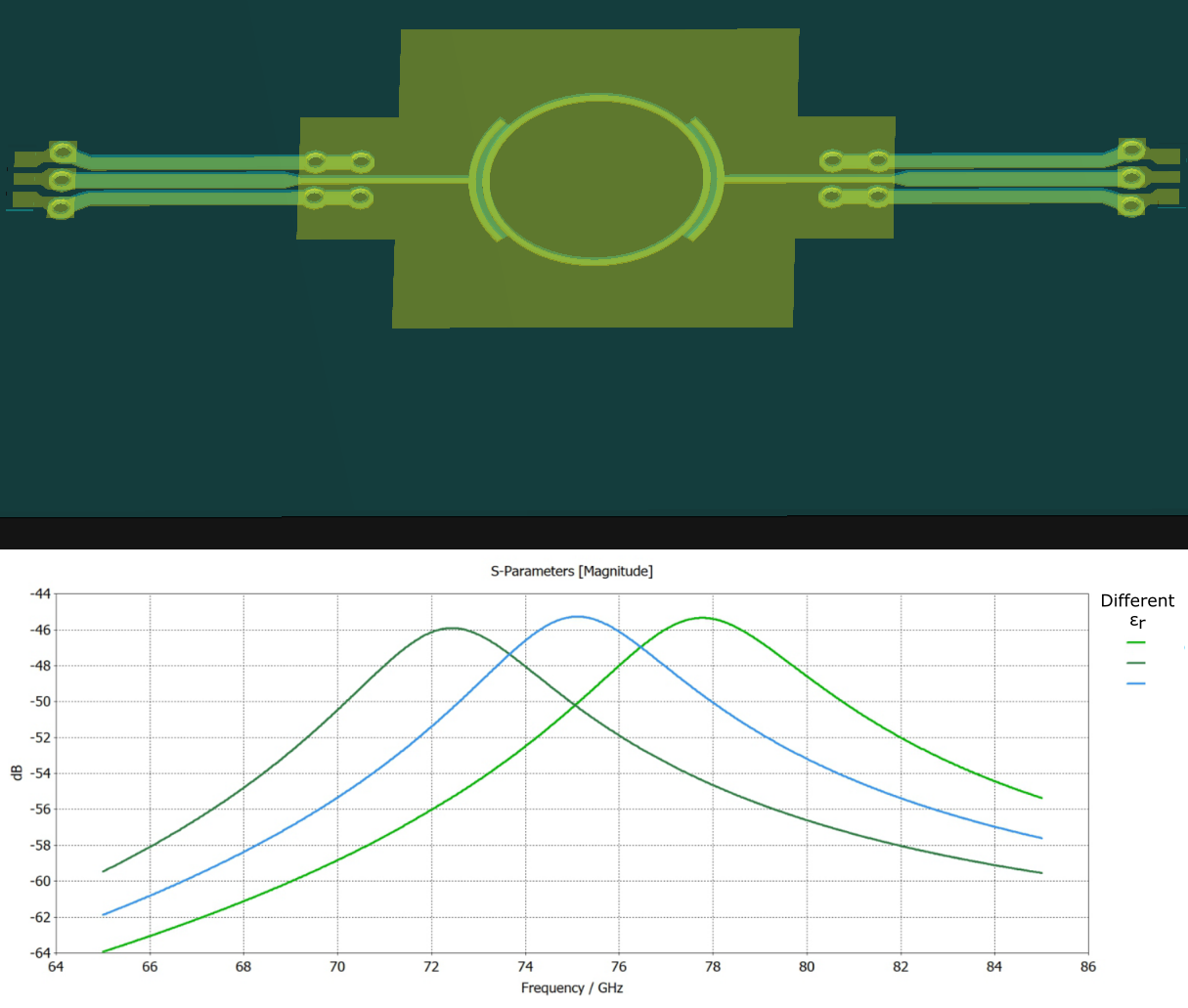

MMIC Sidequests

MMIC Nebenquest

E-Band Current Clamping PA

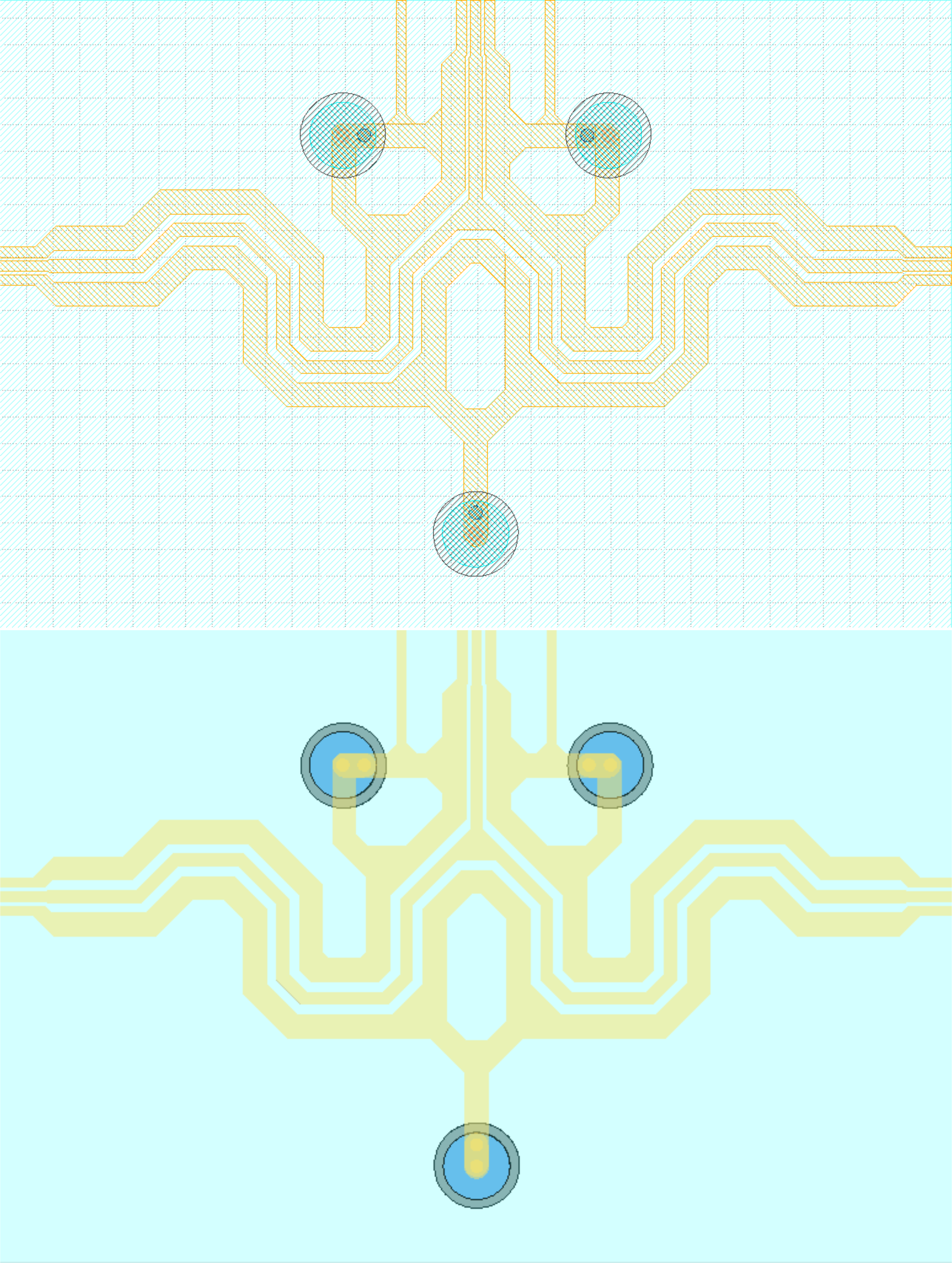

x4/x8 Multiplier

x4/x8 freq-Vervielfacher

E-Band Low Power Receiver

E-Band low-PDC Empfänger

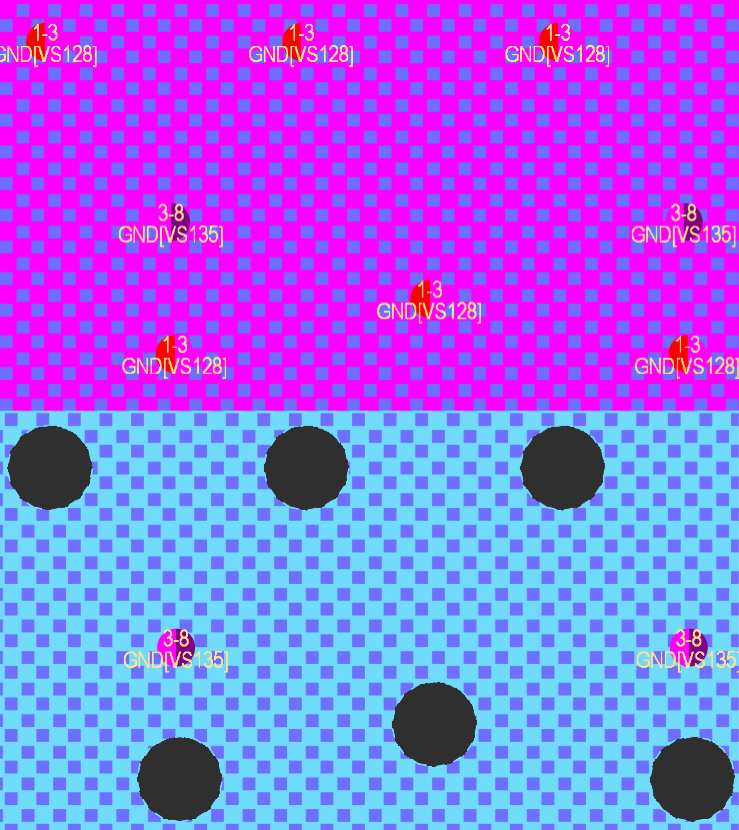

Calibration MMICs

Kalibrier Chips

Scripts

Skripte

Dactyl Manuform

Keyboard Design

Tastatur Design

Keyboard Programming

Tastatur Programmierung

Cellphone Holder

Handyhalter

Holder Design

Halter Design

Holder Customization

Halter Individualisierung

Holder Assembly

Halter Aufbau

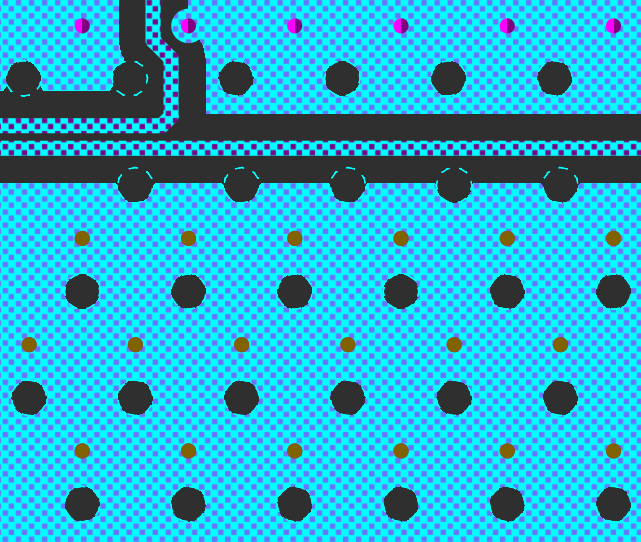

CST

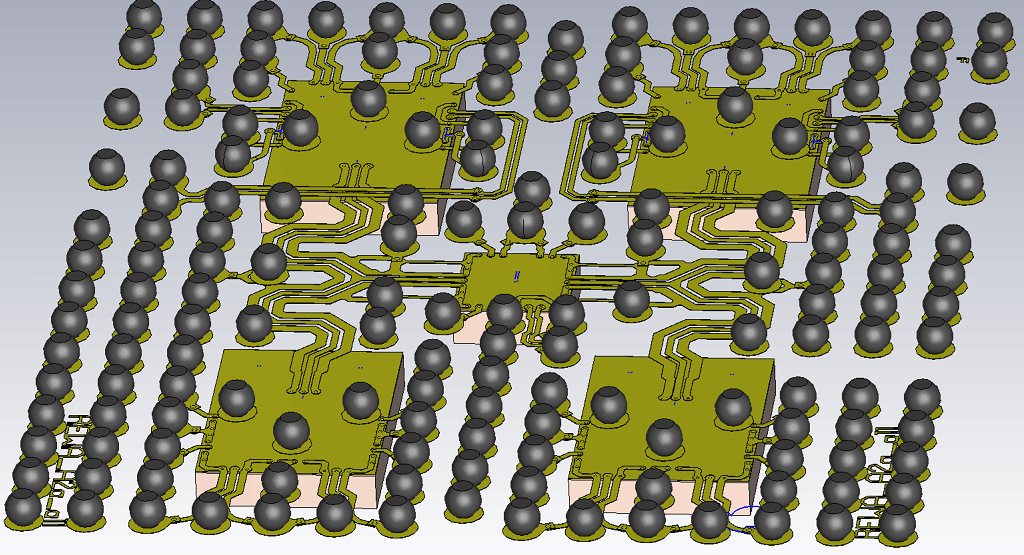

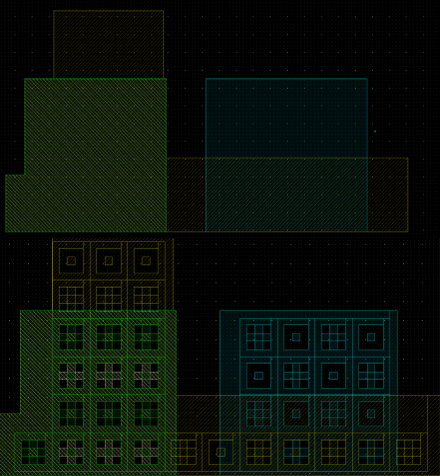

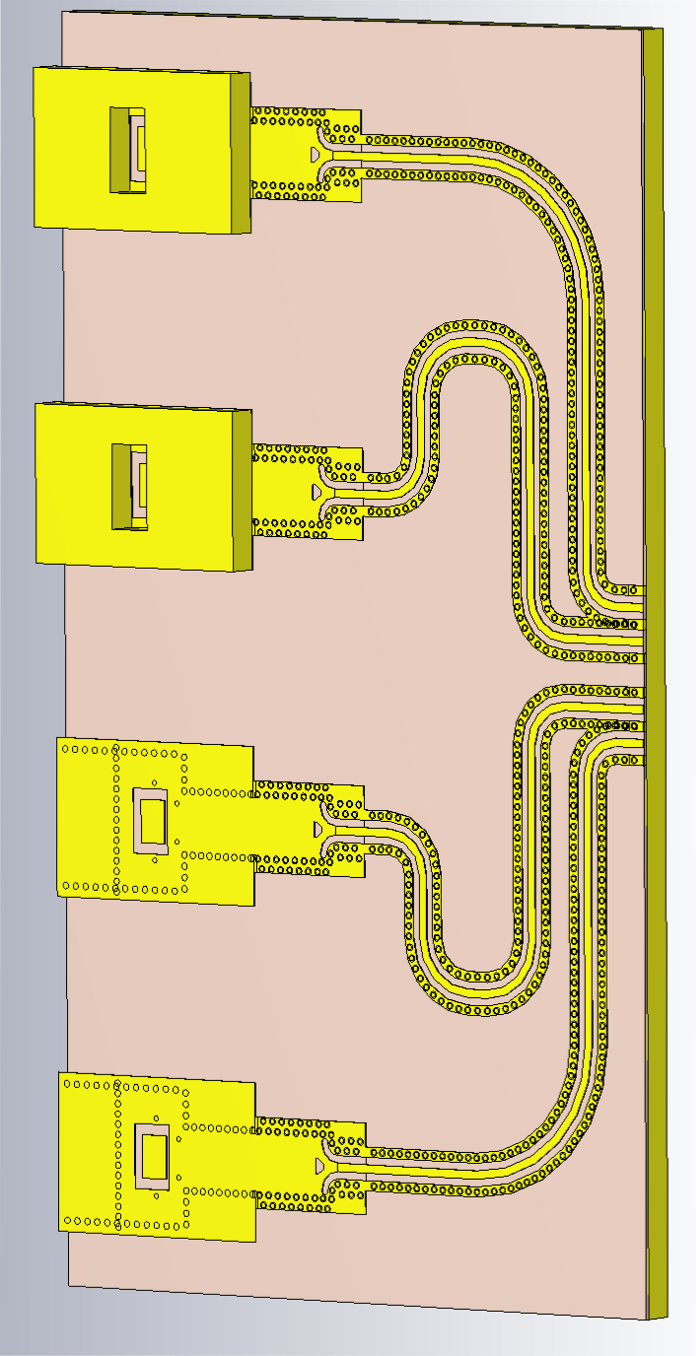

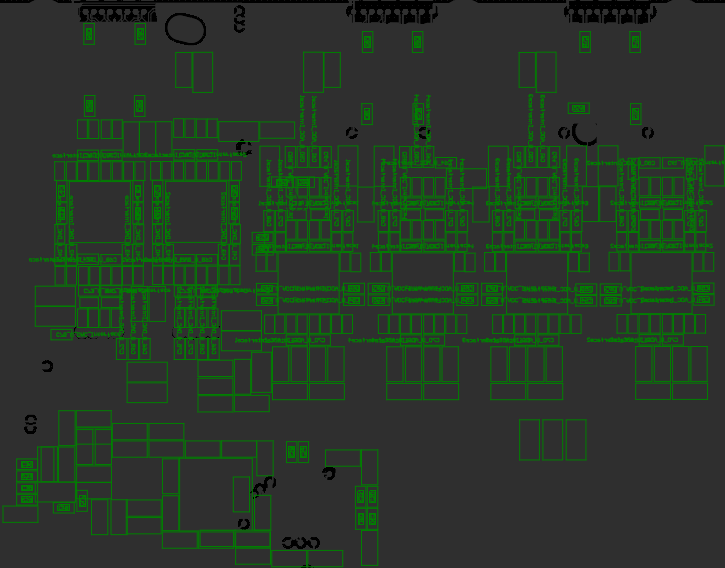

Package Sidequests

Package Nebenquests

Packaged PA

Packaged PA

Packaged Radar Tags

Gepackagete Radar Tags

Packaged D-Band VNAX

Gepackageter D-Band VNAX

Package DRC

LTSpice

Home Dashboard

Haupt Dashboard

Server Tower

Serverturm

Firewall

Cadence

Research Proposals

Forschungsanträge

Sports

Sport

Weight- lifting

Krafttraining

Jogging Club

Freelethics Club

Certified Languages

Sprachzertifikate

German

Deutsch

English

Englisch

Japanese

Linux

Home Server

Heimserver

Daily Drive

Tägliche Benutzung